- 您现在的位置:买卖IC网 > Sheet目录509 > SI4313-B1-FM (Silicon Laboratories Inc)IC RX FSK 315-915MHZ 20VQFN

�� �

�

Si4313-B1�

�6.� Data� Handling�

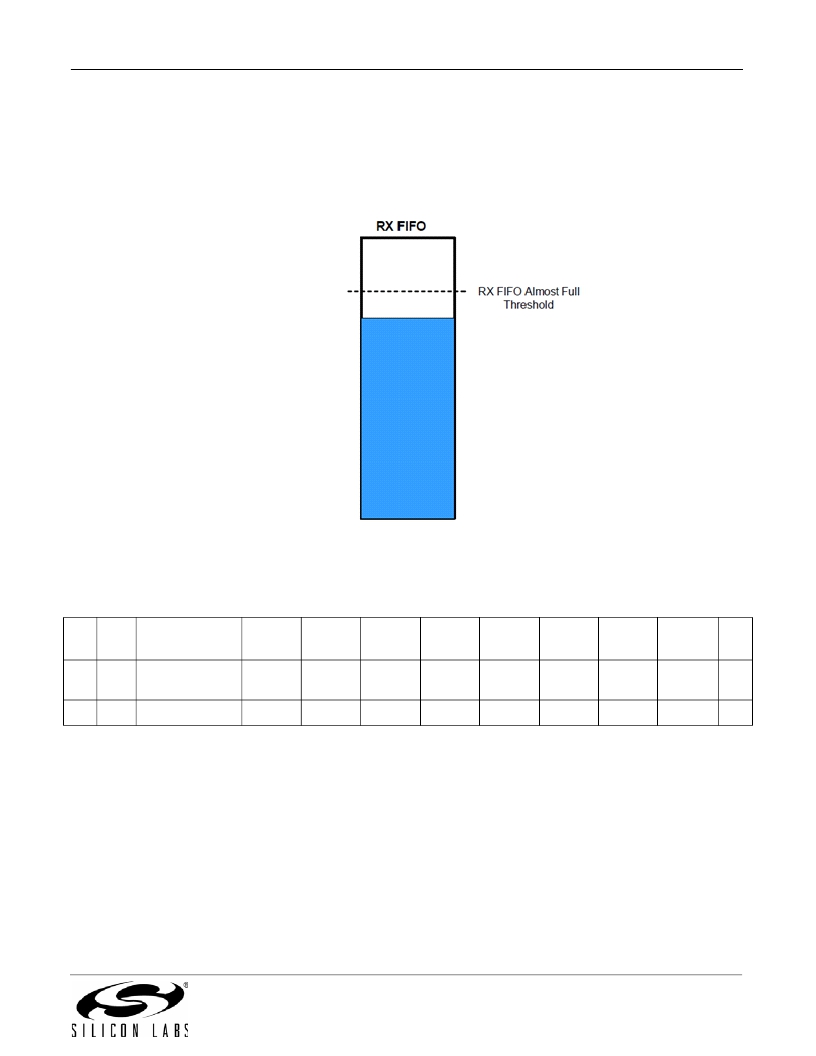

�6.1.� RX� FIFO�

�A� 64� byte� FIFO� is� integrated� into� the� chip� for� RX,� as� shown� below.� "Register� 7Fh.� FIFO� Access"� is� used� to� access�

�the� FIFO.� As� described� in� "3.1.� Serial� Peripheral� Interface"� on� page� 17,� a� burst� read� from� address� 7Fh� will� read�

�data� from� the� RX� FIFO.�

�Figure� 9.� FIFO� Threshold�

�The� RX� FIFO� has� one� programmable� threshold� called� the� FIFO� Almost� Full� Threshold,� rxafthr[5:0].� When� the�

�incoming� RX� data� reaches� the� Almost� Full� Threshold,� an� interrupt� will� be� generated� to� the� microcontroller� via� the�

�nIRQ� pin.� The� microcontroller� will� then� need� to� read� the� data� from� the� RX� FIFO.�

�Add�

�R/W�

�Func/�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�POR�

�Description�

�Def�

�08�

�R/W�

�Operating� &� Func-�

�tion� Control� 2�

�Reserved� Reserved� Reserved�

�rxmpk�

�Reserved�

�enldm�

�ffclrrx�

�Reserved� 00h�

�7E�

�R/W�

�RX� FIFO� Control�

�Reserved� Reserved� rxafthr[5]�

�rxafthr[4]�

�rxafthr[3]�

�rxafthr[2]� rxafthr[1]�

�rxafthr[0]�

�37h�

�The� RX� FIFO� pointers� may� be� reset� with� the� ffclrrx� bit� in� "Register� 08h.� Operating� Mode� and� Function� Control� 2".�

�The� ffclrrx� bit� does� not� delete� the� data� in� the� FIFO,� it� only� resets� the� FIFO� pointers.� All� interrupts� may� be� enabled�

�by� setting� the� Interrupt� Enabled� bits� in� "Register� 05h.� Interrupt� Enable� 1"� and� "Register� 06h.� Interrupt� Enable� 2,".� If�

�the� interrupts� are� not� enabled,� the� function� will� not� generate� an� interrupt� on� the� nIRQ� pin,� but� the� bits� will� still� be�

�read� correctly� in� the� Interrupt� Status� registers.�

�Rev.� 1.0�

�29�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SI4320-J1-FT

IC RCVR FSK 915MHZ 5.4V 16-TSSOP

SI4322-A0-FT

IC RX FSK UNI 868/915MHZ 16TSSOP

SI4324DY-T1-GE3

MOSFET N-CH D-S 30V 8-SOIC

SI4330-B1-FM

IC RCVR ISM 960MHZ 3.6V 20-QFN

SI4354DY-T1-GE3

MOSFET N-CH D-S 30V 8-SOIC

SI4355-B1A-FM

IC EZRADIO FM RECEIVER SI4355

SI4388DY-T1-GE3

MOSFET DUAL N-CH 30V 8-SOIC

SI4390DY-T1-GE3

MOSFET N-CH 30V 8.5A 8SOIC

相关代理商/技术参数

SI4313-B1-FMR

功能描述:射频接收器 240-960 MHz Receiver RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4315-A0-FT

功能描述:射频接收器 Receivers - IA4315 RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4320DY

制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30-V (D-S) MOSFET

SI4320DY-T1

功能描述:MOSFET 30V 25A 1.6W RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320DY-T1-E3

功能描述:MOSFET 30V 25A 3.5W 3.0mohm @ 10V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320DY-T1-GE3

功能描述:MOSFET 30V 25A 3.5W 3.0mohm @ 10V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320-J1-FT

功能描述:射频接收器 Receivers - IA4320 RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4320-J1-FTR

功能描述:射频接收器 Receiver (EZRadio) RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel